Are you asking for 'sar adc thesis'? Here you will find all the details.

Ehsan MazidiEhsan Mazidi The presented thesis is the design and analysis of AN 8-bit successive bringing close together register (SAR) linear to digital converter (ADC), designed for low-power applications so much as bio-medical implants.Author: Ehsan MazidiCreated Date: 2/3/2021 9:35:23 Postmortem

Table of contents

- Sar adc thesis in 2021

- Asynchronous sar adc logic

- Sar adc comparator

- Sar adc design

- Sar redundancy

- Sar adc calibration

- Sar adc redundancy bit

- Successive approximation adc pdf

Sar adc thesis in 2021

This picture representes sar adc thesis.

This picture representes sar adc thesis.

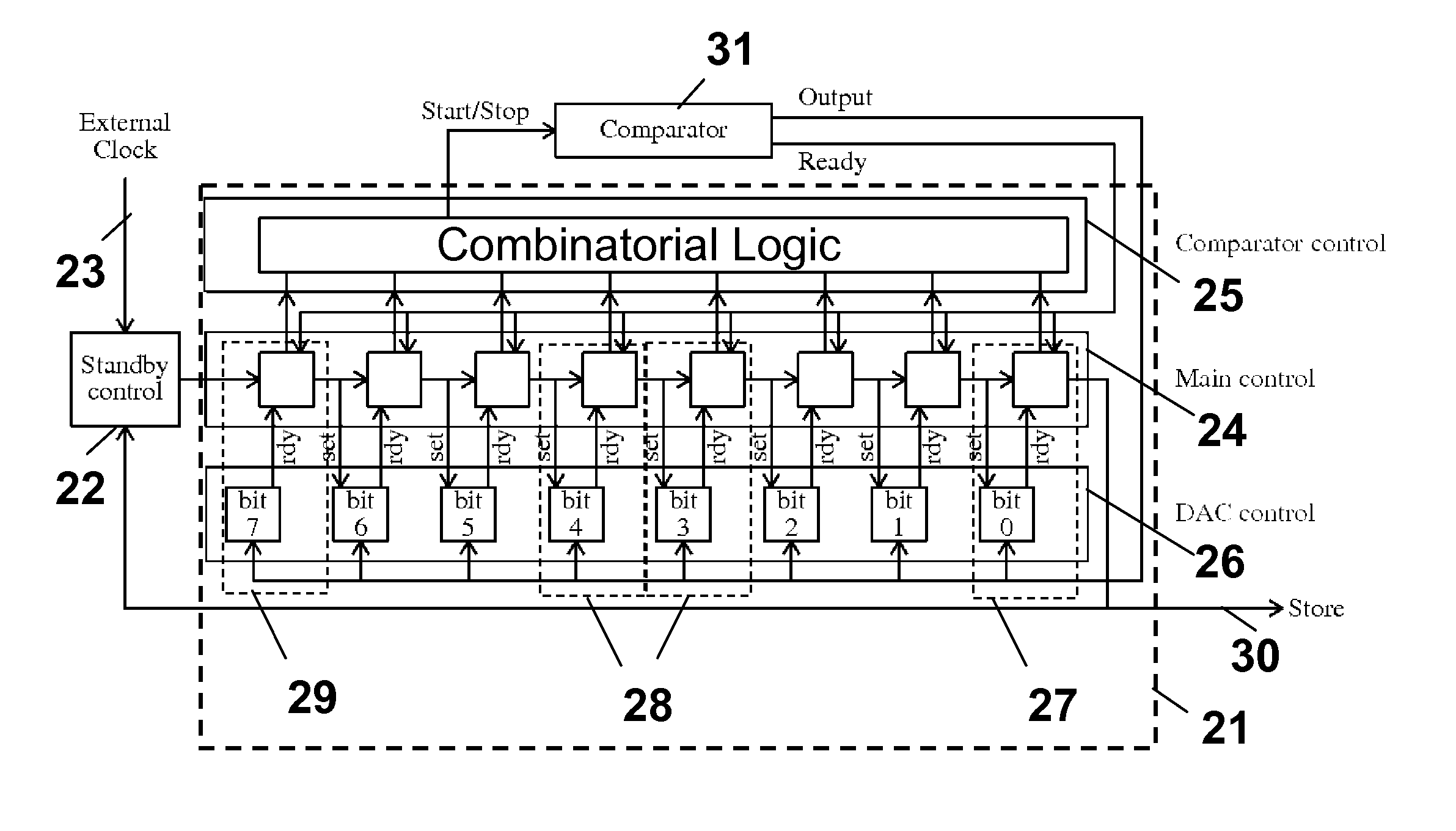

Asynchronous sar adc logic

This picture illustrates Asynchronous sar adc logic.

This picture illustrates Asynchronous sar adc logic.

Sar adc comparator

This picture demonstrates Sar adc comparator.

This picture demonstrates Sar adc comparator.

Sar adc design

This image demonstrates Sar adc design.

This image demonstrates Sar adc design.

Sar redundancy

This picture demonstrates Sar redundancy.

This picture demonstrates Sar redundancy.

Sar adc calibration

This image illustrates Sar adc calibration.

This image illustrates Sar adc calibration.

Sar adc redundancy bit

This picture shows Sar adc redundancy bit.

This picture shows Sar adc redundancy bit.

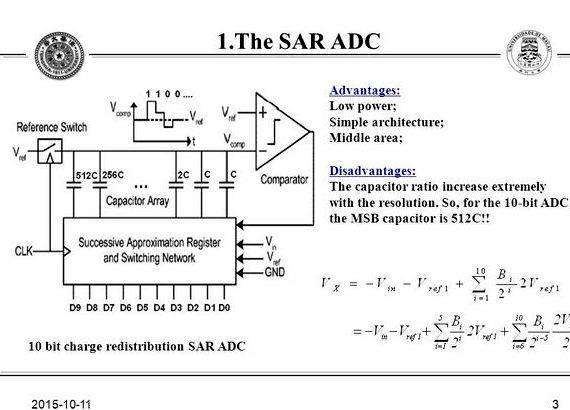

Successive approximation adc pdf

This picture illustrates Successive approximation adc pdf.

This picture illustrates Successive approximation adc pdf.

Why do we need successive approximation registers ( SAR )?

Raheleh Hedayati Abstract In recent years, there has been a growing need for Successive Approximation Register (SAR) Analog-to-Digital Converter in medical application such as pacemaker. The demand for long battery life-time in these applications poses the requirement for designing ultra-low power SAR ADCs.

How is asynchronous SAR used in 28nm CMOS?

The later 6b 46GS/s ADC in 28nm CMOS employs asynchronous SAR sub-ADC design with back-end meta-stability correction. The measurement results show it achieves sparkle-code error free operation over 1e10 samples in addition to achieving >23GHz bandwidth and 25.2dB SNDR.

Which is thesis work focuses on SAR logic?

This thesis work initially investigates and compares different structures of SAR control logics including the conventional structures and the delay line based controller. Additionally, it focuses on selection of suitable dynamic comparator architecture.

Why are asynchronous SAR sub-ADCs often used?

Furthermore, asynchronous SAR sub-ADCs are often used in these designs to push the sampling rate even further. The well-known sparkle-code issues caused by comparator meta-stability in asynchronous SARs can significantly increase the Bit-Error-Rate (BER) of the transceivers unless power hungry error correction coding are implemented in the system.

Last Update: Oct 2021